The Reconfigurable Computing Laboratory provides a hands-on, remotely accessible environment that directly supports research in heterogeneous computing, accelerator-based systems, and end-to-end system design. The laboratory infrastructure is designed to support both in-person and remote participation, enabling scalable training and broad access for students and external participants.

The lab is equipped with a 36-core Intel Xeon Gold 6140 2.3GHz CPU coupled with 4 Nvidia V100 GPUs with 640 Tensor cores and 2 Xilinx Alveo U250 Data Center Accelerator Cards (FPGA). This platform is used for hands-on training and experimentation in accelerator programming, performance analysis, and runtime resource management for dynamic workloads.

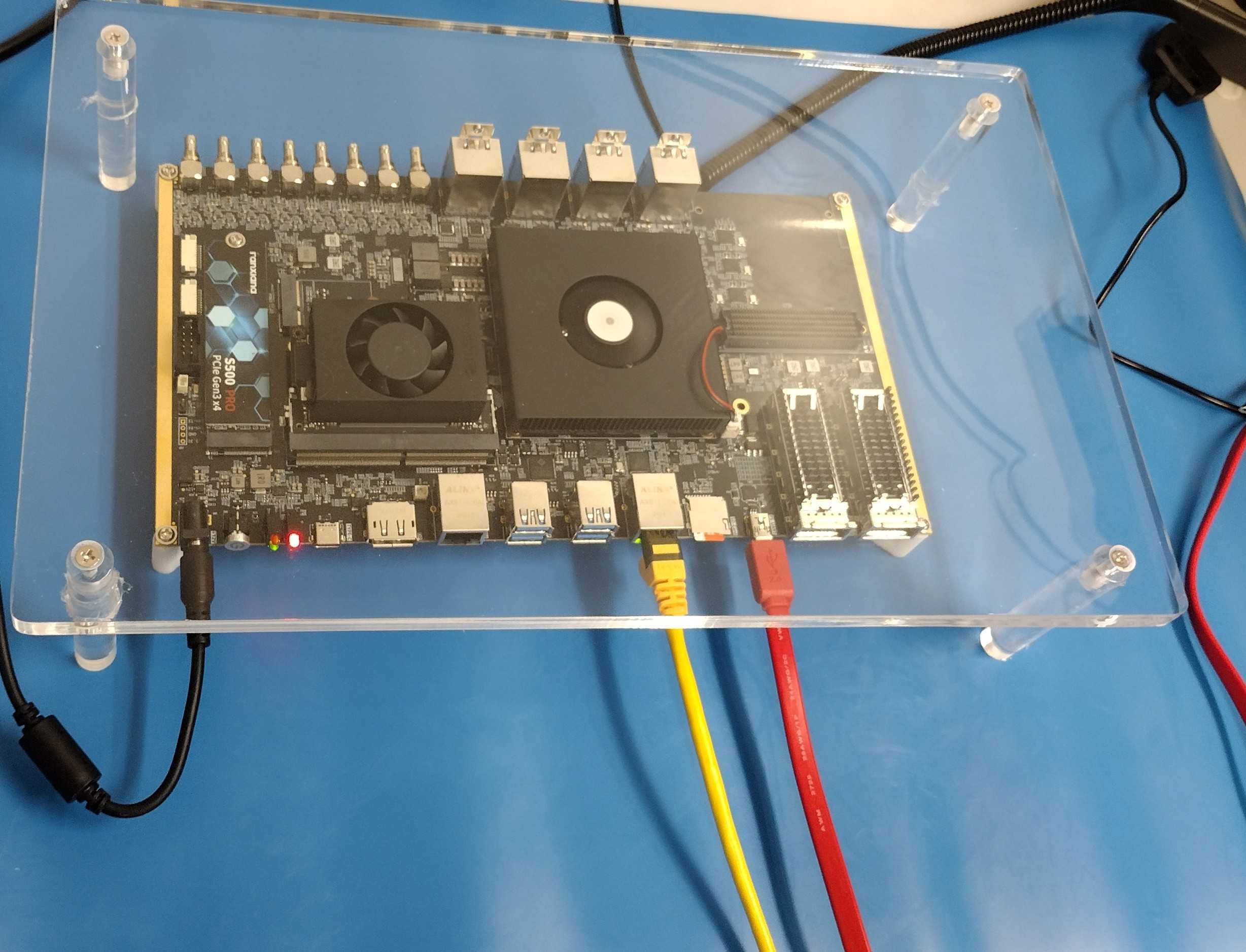

To support edge-scale and embedded heterogeneous systems, the lab also maintains a Z19-M development platform integrating an AMD Zynq UltraScale+ MPSoC (XCZU19EG) with an NVIDIA Jetson Orin NX module. This FPGA–GPU coupled platform enables training modules focused on heterogeneous system integration, accelerator orchestration, and end-to-end system design.

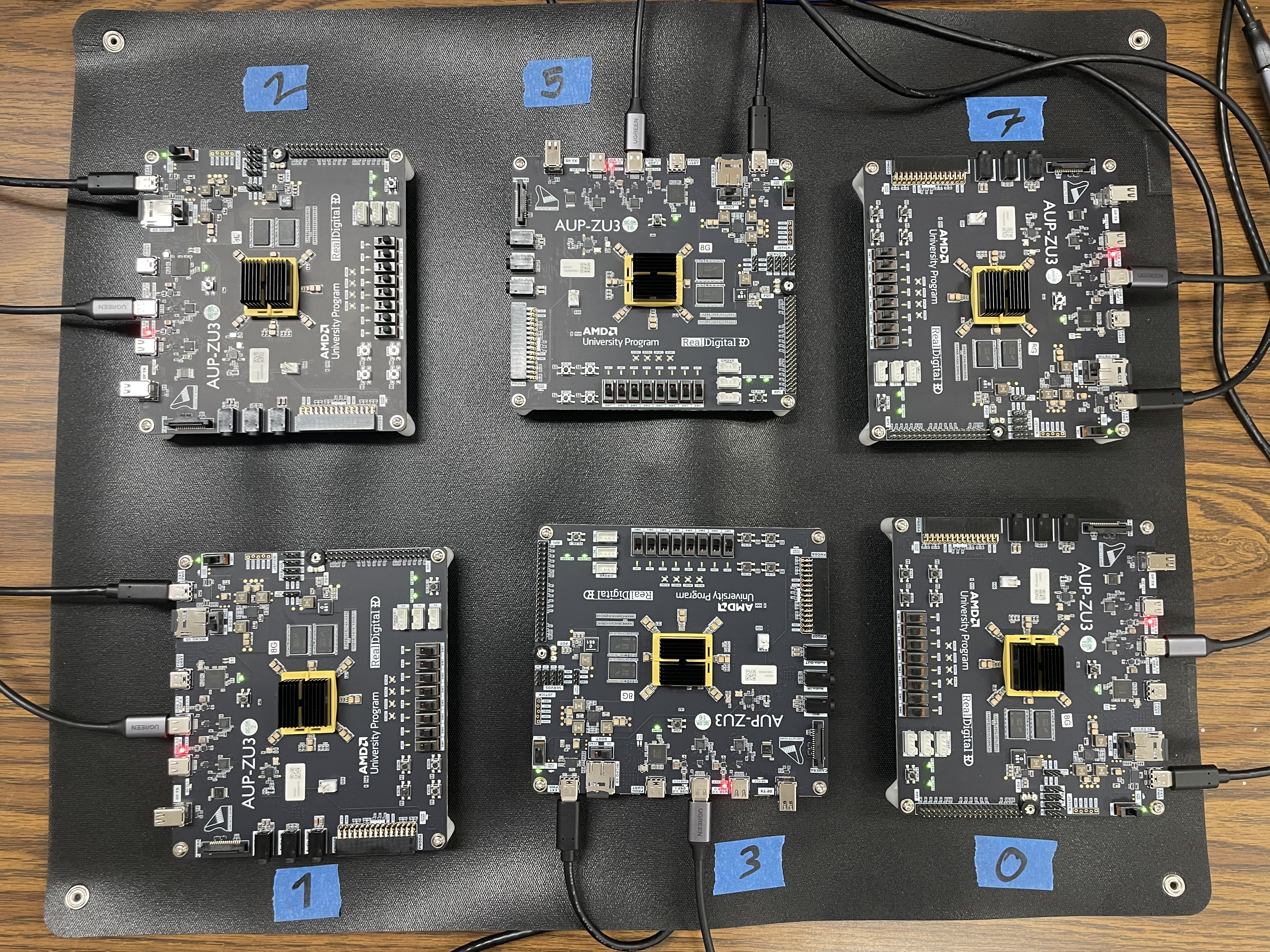

The laboratory includes a diverse set of FPGA and SoC platforms used for modeling, emulation, and prototyping of domain-specific architectures. These include four Zynq UltraScale+ MPSoC ZCU102 boards, two Xilinx VCU128 boards, two Alveo U250 accelerator cards, and eight AUP-ZU3 boards. Notably, the AUP-ZU boards are fully accessible remotely and are integrated into the lab’s shared experimental infrastructure.

These remotely accessible platforms are utilized in graduate-level Reconfigurable Computing course taught by Akoglu, where student teams conducted heterogeneous systems research projects involving FPGA-based acceleration, system integration, and performance evaluation. This prior instructional use demonstrates both the maturity of the infrastructure and its suitability for scalable, hands-on training activities that extend beyond a single institution.

Through participation in the AMD University Program, the lab has access to a full suite of FPGA development tools and over 50 FPGA development boards, supporting concurrent student use and rapid deployment of new training modules.

Together these facilities provide a comprehensive, scalable, and proven environment for delivering hands-on research and training in heterogeneous computing.