University of Arizona Reconfigurable Computing Lab (UA-RCL)

Our work sits at the intersection of computer architecture, system software, and domain-specific computing. We build the runtimes, compilers, schedulers, and hardware architectures that allow heterogeneous computing systems to be programmed, managed, and optimized in a unified, portable, and hardware-agnostic way from the embedded edge to high-performance platforms. If you want to see what it looks like when hardware diversity becomes a feature instead of a burden, explore our projects.

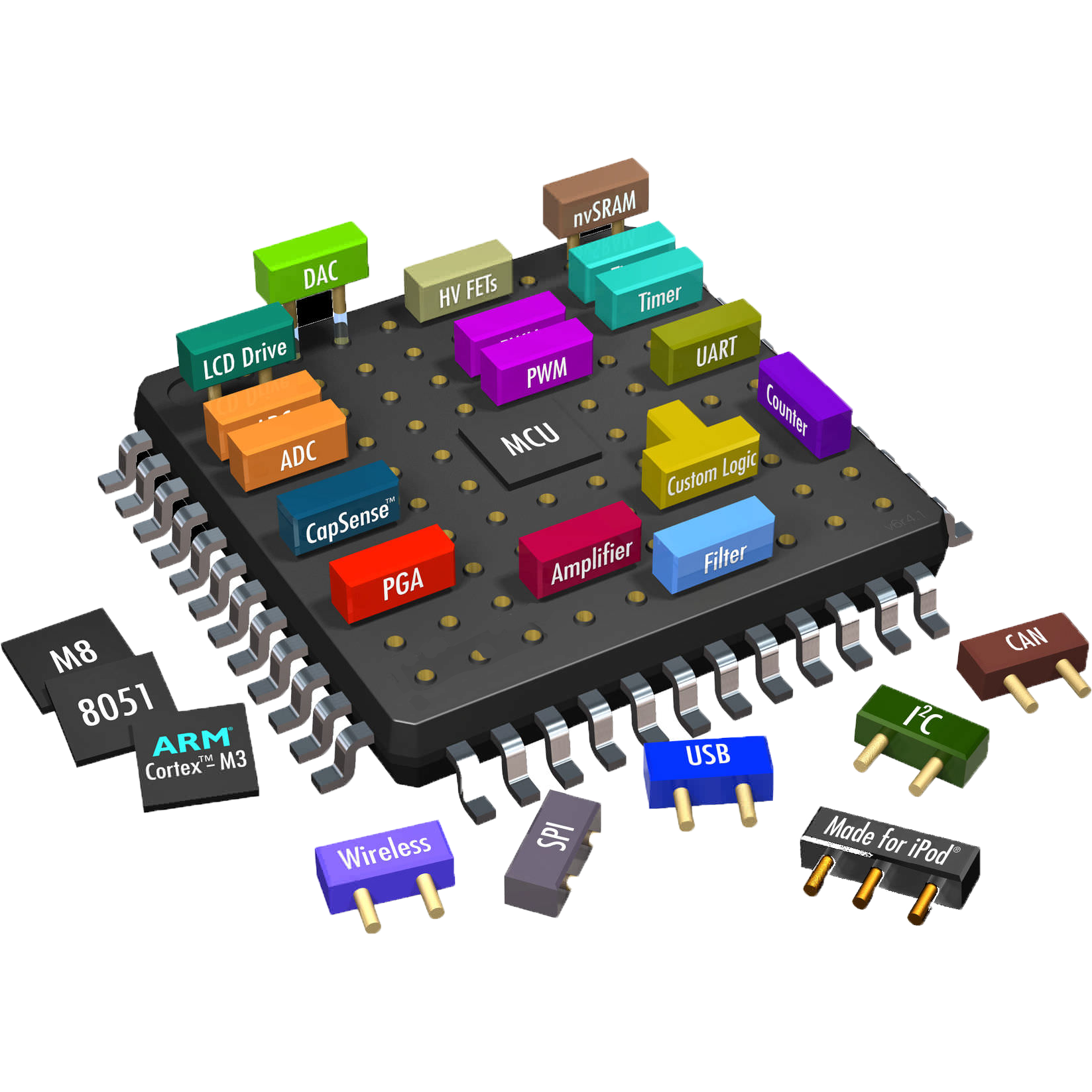

Monolithic systems are architecturally rigid, making them poorly suited to diverse and dynamically evolving workloads. In such environments, execution efficiency and adaptability matter more than raw compute density. Heterogeneous architectures address this need by combining the complementary strengths of multiple computation models. Systems that couple CPUs with accelerators such as GPUs and FPGAs have already become mainstream, and the trajectory is clear. Architectures are evolving toward deeper heterogeneity with the integration of specialized processing elements such as NPUs, TPUs, and CGRAs. Yet as heterogeneity increases, so does complexity.

Researchers and system architects face mounting challenges in exploring the vast design space of processing element compositions, scheduler heuristics, and runtime strategies, and the tools needed to do so in a unified environment simply do not exist. Another critical challenge is in optimizing performance without sacrificing programming productivity, and the software and runtime infrastructure needed to harness this diversity remains fragmented, architecture-specific, and largely inaccessible. The UA-RCL exists to close this void.

News

- Mustafa Ghanim and Serhan Gener presented a poster and demo at the 2026 Big Idea Challenge Research Showcase as members of the AZSCI team. (Check out our blog post)

- Our paper titled Event-based Human Action Recognition: Rehabilitation Monitoring Dataset and Models is published in International Conference on Future Machine Learning and Data Science (FMLDS’25). This paper is available on (IEEE Xplore).

- Our paper titled K-PACT: Kernel Planning for Adaptive Context Switching — A Framework for Clustering, Placement, and Prefetching in Spectrum Sensing is published in International Conference on Computer-Aided Design (ICCAD’25). The paper is available on (IEEE Xplore) and the source code is hosted on Github.

- Our paper titled A Portable Framework with Generalized Runtime Features for Task Graph Execution and Concurrent Multi-Application Deployment on Heterogeneous Systems (Science Direct) is published in Future Generation Computer Systems as journal preproof.

- Our paper titled HOPPERFISH: Holistic Profiling with Portable Extensible and Robust Framework Intended for Systems with Heterogeneity is accepted for publication in ACM Transactions on Architecture and Code Optimization and is available as just accepted in ACM. The source code is hosted on Github.

- Our paper titled An Overview of Challenges and Requirements for Real-Time Spectrum Sensing in Modern RF Autonomy Systems (IEEE Xplore) is published in IEEE Design & Test.

- Our paper titled RIMMS: Runtime Integrated Memory Management System for Heterogeneous Computing is accepted for publication in Embedded Systems Week (ESWEEK’25) and is available as just accepted in ACM Transactions on Embedded Computing Systems as part of ESWEEK’25 special issue.

- Our paper titled A Unified Portable and Programmable Framework for Task-Based Execution and Dynamic Resource Management on Heterogeneous Systems (ACM) was published in Extreme Heterogeneity Solutions (ExHET’25).

- Our paper titled A Unified Portable and Programmable Framework for Task-Based Execution and Dynamic Resource Management on Heterogeneous Systems has won the Best Paper Award in Workshop on Extreme Heterogeneity Solutions (ExHET’25)! Congratulations Serhan! (Check out our blog post)

- Serhan Gener and Sahil Hassan held a Tutorial Session titled CEDR: A Holistic Software and Hardware Design Environment for Hardware Agnostic Application Development and Deployment on FPGA-Integrated Heterogeneous Systems in ISFPGA’25. (Check out our blog post).

- Our paper titled A Runtime Manager Integrated Emulation Environment for Heterogeneous SoC Design with RISC-V Cores (IEEE Xplore) was published in Heterogeneity in Computing Workshop (HCW’24).

Click here to check out archived news.

Open-Source Highlights

CEDR: a Compiler-integrated Extensible DSSoC Runtime

CEDR is an open-source, compiler-integrated, extensible DSSoC runtime that unifies a front-end compilation flow with a Linux-based runtime and intelligent scheduling framework. Applications are transformed into hardware-agnostic function calls, allowing the runtime to dynamically map tasks to the most suitable processing elements, enabling efficient resource utilization and productive deployment in heterogeneous systems.

RANC: Reconfigurable Architecture for Neuromorphic Computing

RANC is a highly flexible environment that enables rapid experimentation with neuromorphic architectures in both software via C++ simulation and hardware via FPGA emulation. RANC enables hardware architects and application engineers to investigate and tune parameters of their neuromorphic architecture that would otherwise be unavailable on a purely prefabricated ASIC.

K-PACT: Kernel Planning for Adaptive Context Switching

K-PACT is a software planning framework that clusters temporally independent kernels and places them onto reconfigurable hardware equipped with multiple IMEM banks, enabling nanosecond-scale context switching without requiring full hardware reconfiguration. This capability is particularly critical for dynamic workloads, where rapid adaptation and efficient reuse of resources are essential.