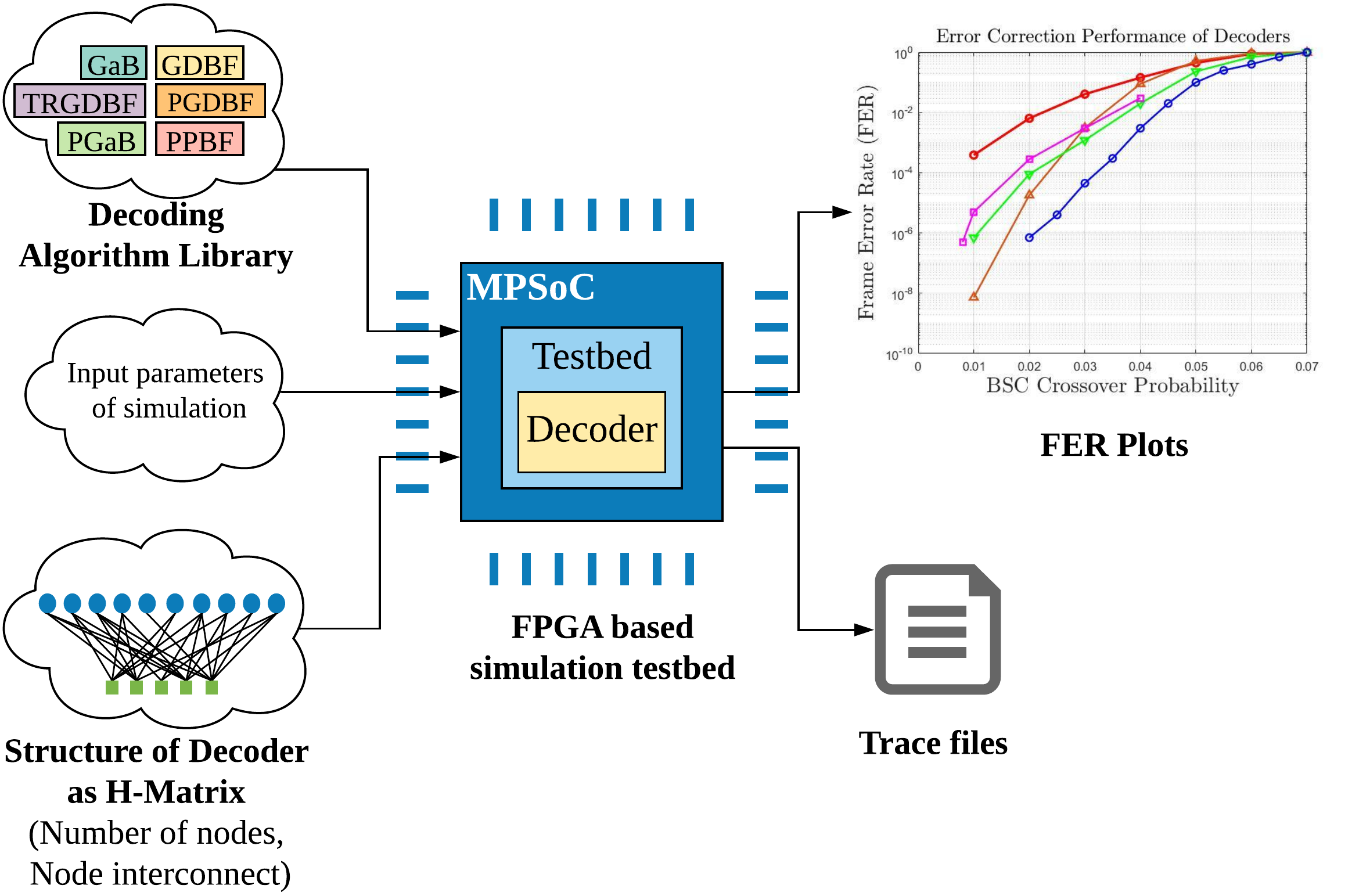

This project presents an FPGA based high throughput and modular simulation testbed for rapid simulation of decoders for Low Density Parity Check (LDPC) codes. The users can replace different modules of this testbed to incorporate their own hard-decision decoders for rapid characterization.

LDPC codes are a popular choice for employment in several cutting edge communication standards such as 5G, WiFi, WiMax, 10 Gigabit Ethernet etc.. With the increasing popularity of LDPC codes, the research to obtain decoders with better error correction performance and reduced hardware footprint is becoming prominent as well. Analyzing and improving the decoders require detailed large scale simulations. General purpose CPU based software execution of such simulators have become infeasible due to long simulation time. Furthermore, developing such simulators on hardware platform (e.g. FPGA) requires significant amount of effort which is outside the scope of research on decoders.

The testbed reduces the duration of large scale simulations down to order of hours from order of years on a single core CPU. Furthermore, this highly flexible testbed reduces design time significantly by enabling users to easily integrate their desired decoders with this platform.

Currently, our testbed supports several hard-decision decoding algorithms such as Gallager B (GaB), Probabilistic GaB (PGaB), Gradient Descent Bit Flipping (GDBF), and Probabilistic GDBF (PGDBF). The FPGA based testbed allows users to specify different simulation parameters before launching the execution, and returns the statistics to the user for calculating the error correction performance of decoder under test.

In future works, we aim to add more recent hard-decision decoding algorithms like Probabilistic Parallel Bit Flipping (PPBF), Tabu-list Random-penalty GDBF (TRGDBF) etc. to the decoder library. We further aim to take the testbed on MPSoC. Taking advantage of this platform, the aim is to make the testbed more flexible and capable. Besides statistics, it should be able to provide detailed information to the users to identify the weaknesses of the simulated decoders.