## A Runtime Manager Integrated Emulation Environment for Heterogeneous SoC Design with RISC-V Cores

**H. Umut Suluhan**<sup>1</sup>, Serhan Gener<sup>1</sup>, Alexander Fusco<sup>1</sup>, Joshua Mack<sup>1</sup>, Ismet Dagli<sup>2</sup>, Mehmet Belviranli<sup>2</sup>, Cagatay Edemen<sup>3</sup>, and Ali Akoglu<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, University of Arizona {suluhan, gener, jmack2545, afusco1, akoglu}@arizona.edu

<sup>2</sup>Computer Science Department, Colorado School of Mines, Golden, CO, USA {ismetdagli,belviranli}@mines.edu

<sup>3</sup>Electrical and Electronics Engineering Department, Ozyegin University, Istanbul, Turkey cagatay.edemen@ozyegin.edu.tr

#### **Motivation**

- As systems become more heterogenous, stress on runtime system increases

- Task scheduling and resource management

- Runtime overhead and scalability

- RISC-V offers ISA and datapath customization

- Enables balancing performance and energy efficiency

- Facilitates workloads that need hardware tailored for specific performance goals

- Can also be utilized for resource management with light-weight RISC-V cores

Reconfigurable

Computing Lab

#### **Contributions**

- Leveraged customizable RISC-V cores to realize a scalable runtime system

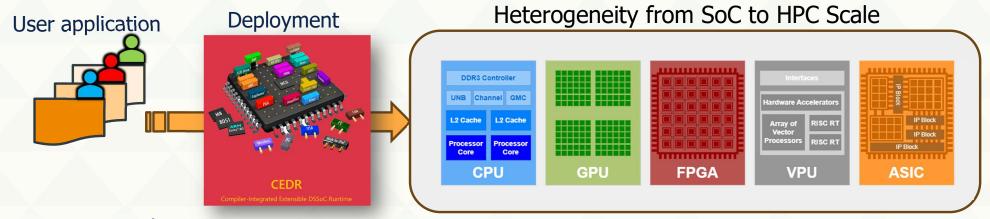

- Demonstrated ability to deploy dynamic workloads on a RISC-V integrated heterogenous system using CEDR\*

Link to the open source CEDR ecosystem

Hardware Agnostic Application Development and Deployment\*

GENERAL DYNAMICS

Mission Systems

ARM'19

FOSDEM'20

GNU

Radio'20

FOSDEM'21

GNU Radio'22 ESWEEK'23 ISFPGA'24

Reconfigurable

Computing Lab

\*Mack et al., "CEDR-API: Productive, Performant Programming of Domain-Specific Embedded Systems," Lectrical & Computer HCW'23 DOI:10.1109/IPDPSW59300.2023.00016

\*Kumbhare et al., "User-Space Emulation Framework for Domain-Specific SoC Design," HCW'20 http://dx.doi.org/10.1109/IPDPSW50202.2020.00016

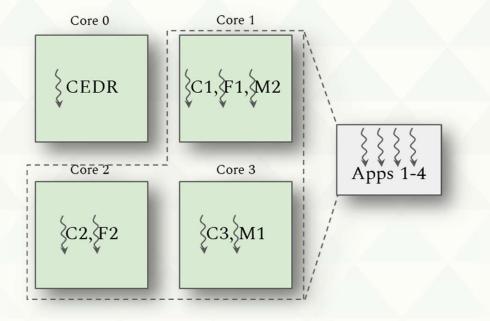

## Scalability Limitation of Runtime System

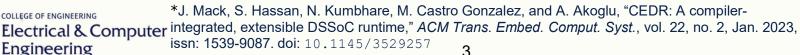

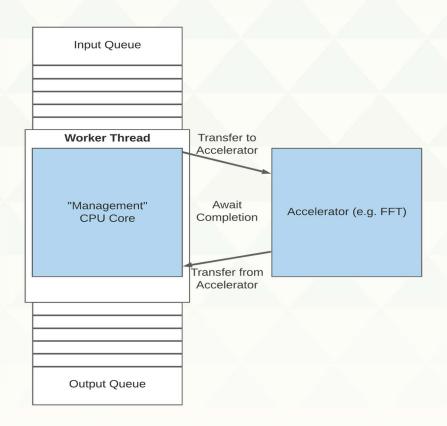

**CEDR Worker Thread Overview**

Scenario: 3 Cores (C1-C3), 2 FFTs (F1, F2), 2 MMULTs (M1,M2) as worker threads for 4 concurrent apps → Cores 1-3: 3.67 threads/Core

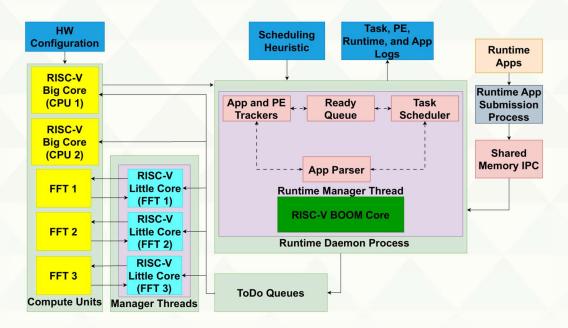

## **CEDR RISC-V Integration**

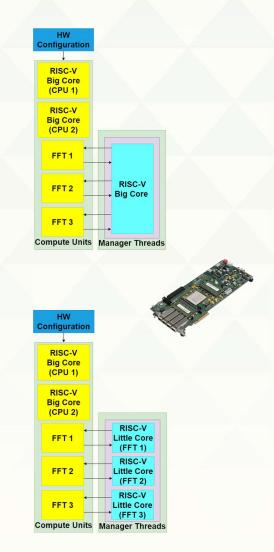

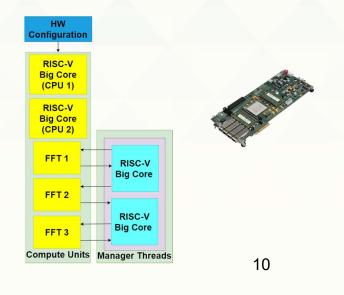

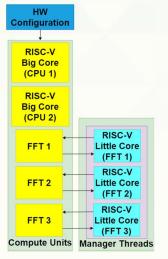

CEDR workflow with BOOM core for runtime manager thread, 3 "little cores" for managing the 3 FFT accelerators, and two "big cores" as CPU compute resources.

| Hardware Unit | Parameter           | BOOM         | Big      | Little |

|---------------|---------------------|--------------|----------|--------|

|               | Branch Prediction   | ✓            | <b>√</b> | X      |

| CPU           | Floating Point Unit | $\checkmark$ | ✓        | X      |

|               | Out-of-Order        | <b>√</b>     | X        | X      |

|               | nSets               | 64/64        | 64/64    | 32/32  |

| DCache/ICache | nWays               | 4/4          | 4/4      | 1/1    |

| Deache/Teache | nTLBSets            | 1/1          | 1/1      | 1/1    |

|               | nTLBWays            | 8/32         | 32/32    | 8/8    |

|               | blockBytes          | 64/64        | 64/64    | 64/64  |

#### Configuration of RISC-V Cores

- Little cores handle accelerator management

- low overhead execution

- improves scalability

## **Experimental Setup**

| Hardware    | Number   | LUT         | LUTRAM      | DSP         |

|-------------|----------|-------------|-------------|-------------|

| Unit        | of Units | Utilization | Utilization | Utilization |

| FFT         | 3        | 1.68%       | 1.06%       | 1.21%       |

| BOOM Core   | 1        | 21.70%      | 0.76%       | 1.29%       |

| Big Core    | 2        | 8.60%       | 0.27%       | 0.54%       |

| Little Core | 3        | 3.96%       | 0.15%       | 0.21%       |

#### **Resource Pool**

- 2 CPUs

- 3 FFT Accelerators

#### Utilization per Hardware Unit

#### **Workload Composition**

- Radar Correlator

- Pulse Doppler

- WiFi-TX

- Synthetic Aperture Radar

- Lane Detection

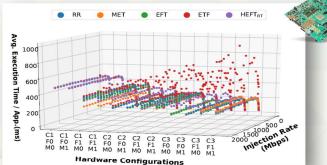

#### Scheduling Heuristics

- Earliest Finish Time (EFT)

- Earliest Time to Finish (ETF)

- Minimum Execution Time (MET)

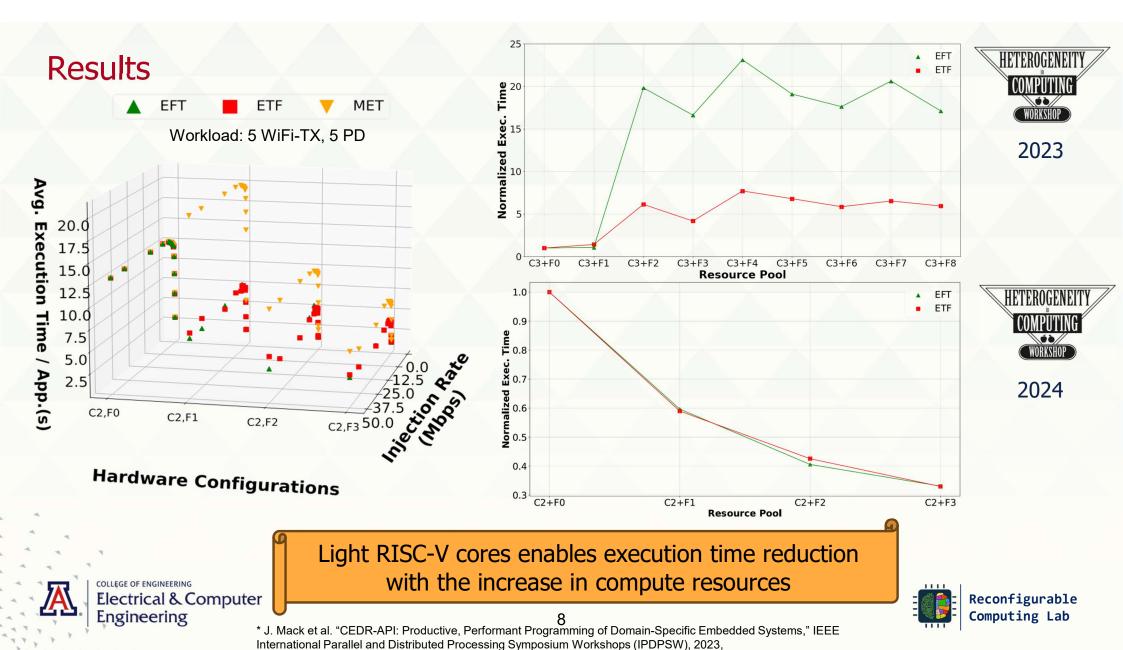

### Results

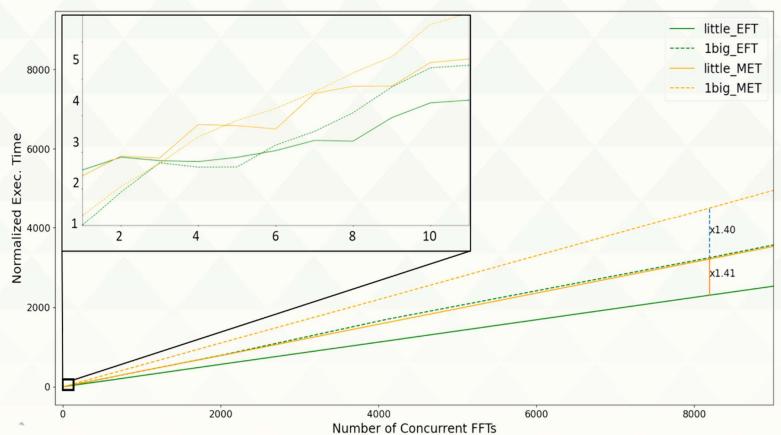

Stress test with FFT only tasks: single big core vs. three little cores

## Results

|         | Number of Tasks | Concurrency<br>Degree | 2big (sec) | 3little (sec) | Speedup | Overhead Reduction |

|---------|-----------------|-----------------------|------------|---------------|---------|--------------------|

| RC      | 3               | 1x3                   | 0.191      | 0.202         | 0.95x   | 3.29%              |

| WiFi TX | 100             | 10x10                 | 3.291      | 2.939         | 1.12x   | 29.55%             |

| PD      | 512             | 256x1 128x2           | 12.590     | 7.395         | 1.70x   | 36.61%             |

| SAR     | 2,305           | 256x3 512x3           | 17.641     | 8.642         | 2.04x   | 47.31%             |

| LD      | 6,148           | 256x24                | 46.03      | 20.35         | 2.26x   | 41.99%             |

Big cores vs Little cores for distributed accelerator management

#### Conclusions and Future Work

- Designed and developed an ecosystem that will serve application engineers and hardware architects for rapidly experimenting with RISC-V integrated heterogeneous systems.

- Showcased the versatility of CEDR framework capable of managing resources for RISC-V integrated heterogeneous systems

- Investigated the trade-off between centralized and distributed accelerator management

- Future Work

- Integrate richer set of RISC-V cores with customized datapaths to support pipelined and dataflowcentric computations

- Utilize customized RISC-V cores for handling accelerator-to-accelerator data flow management

# Thank you!

Contact: {suluhan, gener, akoglu}@arizona.edu